2018年7月25日

FO-PLP製造工程及び主な技術課題についての紹介

3D Packaging and Integration日本地区技術委員会

共同委員長:釣屋 政弘(iNEMI)、島本 晴夫(AIST)

今月号では、FO-PLP(Panel Level Packaging)の製造工程について述べるが、本題に入る前に、パッケージ技術の推移も紹介したい。

パッケージ技術の推移

パッケージの主な役割は半導体チップの保護とチップ上の配線端子の引き回しである。パッケージに使われる材料は、銅や42アロイのリードフレームが主であるが、基板には、過去にはセラミックだったものが、近年では有機基板が多く使われるようになった。マザーボードへの搭載には挿入型もあるが現在は主に表面実装型である。半導体チップ上のパットからワイヤーボンディングやバンプ接続により、基板やリードフレームと電気的接続を取っていた。エレクトロニクス製品の小型化に伴いパッケージも軽薄短小化が求められ、チップサイズと同じパッケージが開発されたり、半導体チップの引き回しを従来のワイヤーボンディングに依るのではなく基板上の再配線技術で行うFan-outパッケージ技術が注目を浴びる様になった。

FO-WLPやFO-PLPの標準化の検討

当技術委員会で主にSEMI規格の開発に注力を注いでいるのは、これらFan-out タイブのWafer Level Package (FO-WLP) やPanel Level Package (FO-PLP)である。パッケージ製造工程は従来のウェハ製造工程とパッケージ組立工程に明確に分かれるのではなく、半導体チップのパットピッチの再配線をウェハ工程の後に継続的に行っていたりしており、ファウンドリー企業がこの分野での製造を担う様になってきている。TSMCが開発したInfoのパッケージ技術の例がある。

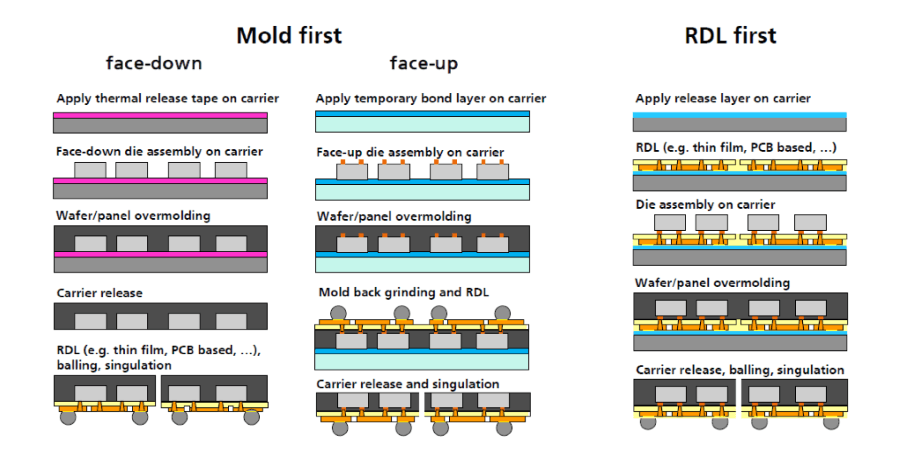

再配線する工程においても幾つかの方法があり、その一例を下記図1に示す。Carrierの上に半導体チップを上向きか下向きに搭載して再配線を行う方法と、Carrier上にまず再配線を施したのちに半導体チップを搭載する方法を示している。その他にも多種多様の手法を用いたパッケージ技術が存在している。

図1: PLP製造プロセスによる分類

主な装置や材料

次に製造工程毎に使われている主な装置や材料等について説明する。

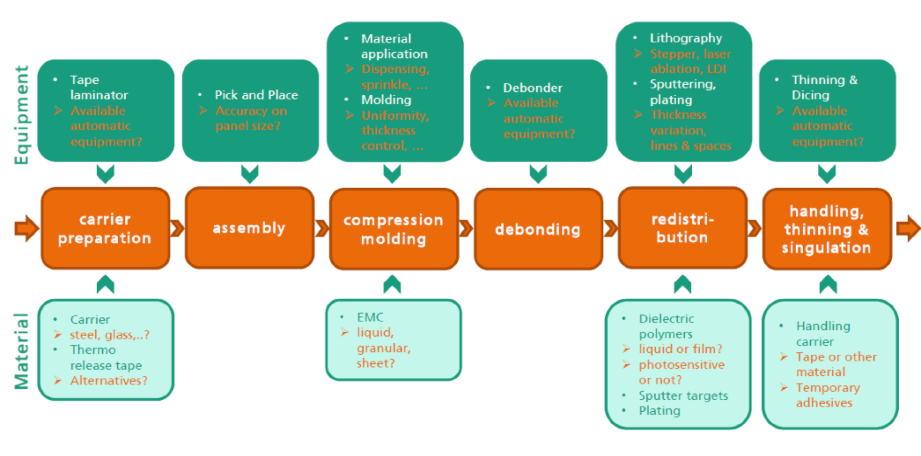

図2は製造工程のフローである。最初の工程は、Carrierを準備して、そのCarrier上に半導体チップを搭載するAssembly工程があり、搭載した半導体チップを保護する封止工程がある。その後にCarrierをはがし、Carrier面に接していた半導体チップのパットから再配線を行い、最後の工程で封止した部分の研磨による薄型化の工程を行い、出荷準備となる。各工程での必要な作業を見ていく。

図2:PLPの主な製造プロセスと主な作業内容

Carrier材料:

Metal/Steel, GlassやPolymerが使われている。Metal/Steel材は主にChip Firstに使われており、多種のCTE値の材料がある。温度・機械特性の安定性が良く、機械加工しやすく、再利用もできる。不利な点は重量が重く、大きなサイズには不利である。Glass材は、RDL Firstに使われており、多種のCTE値の材料がある。温度特性は良いが壊れやすいため機械加工が難しく再利用に難点がある。ポリマー材は、有機基板の様にフィラーを含有する事でCTEが調整できる。再利用はできない。

材のCTEは封止材のChemical Shrinkageと共に封止工程後のDie Shiftへ影響を及ぼす。次回のSEMI通信でさらに詳しくCarrier材の特性について紹介する。

Assembly 工程:

BGA基板と異なりFO-PLP Substrateの広い面積への半導体チップ搭載となると、搭載速度や一つのパネルへのチップ搭載時間も問題となってくる。また、PLP基板のパットピッチや配線幅等が小さくなるため、搭載精度も難しくなる。CarrierのCTE等の影響により温度による影響を大きく受けることになり、Die Shiftの問題も発生する。今後は半導体シリコンチップだけでなく、MEMSやLEDなど多種のコンポーネントを扱うこともあるので、異なる材料をうまく使うことが求められる。

封止工程:

WLPに使われている。作業環境はクリーンルームに近い環境を必要とする。大きいサイズのパネルには液状を塗布する際のパターンが複雑化してくる。また、より長いスパイラルフローの特性が必要となる。粉末タイプは、BGAパッケージに長らく使われており、従来の作業環境で良い。シートタイプは最近注目を集めている材料である。封止材料の特性については、今後のSEMI通信で、その特性を紹介する予定である。広いパネルへの封止方式はCompression Moldingが使われるが、幾つかの課題がある。塗布パターン、フローマーク、ダイシフト及びパネルの反り等が挙げられる。

再配線工程:

WLP用の更なるRDL技術革新が必要となる。再配線用の表面の平坦度の確保の為の液状樹脂の塗布技術やドライフィルムでのラミネート技術が重要である。また、パターン形成技術でも大きいパネルサイズへのレーザや露光技術もファインパターン等に対応する必要がある。

薄型化:

Carrierの有無や半導体チップの有無による違いもあるが、TTV管理が必要である。大きいサイズのパネルの取り扱いへの対応が必要となる。PI&C委員会ではPLP Panel用のFOUPのSEMI規格化の活動を開始している。

3D Packaging and Integration技術委員会では、その規格開発対象をFan-Out Wafer Level PackageやPanel Level Packageに広げて標準化活動を推進している。SEMI規格が必要と思われる分野について、日本地区では、隔月でSteering Groupの会議を開催して議論している。SEMI通信へは技術委員会の活動報告や技術課題等を定期的に掲載し、より多くの方々に本標準化活動へ興味を持っていただき、さらに参画されることを期待している。

本件についての問合せ

SEMIジャパン スタンダード&EHS部

柳澤智栄(cyanagisawa@semi.org )

SEMIジャパンのメールマガジン「SEMI通信」

SEMI通信はSEMIジャパンから配信され、業界、市場、技術のトレンドをお伝えする記事と共に、SEMIの展示会、セミナー、スタンダード (標準化活動)、市場統計などの活動の最新情報を提供するメールマガジンです。

セミナーやイベント、市場統計の案内など半導体業界のホットな情報も併せてご覧いただけます。