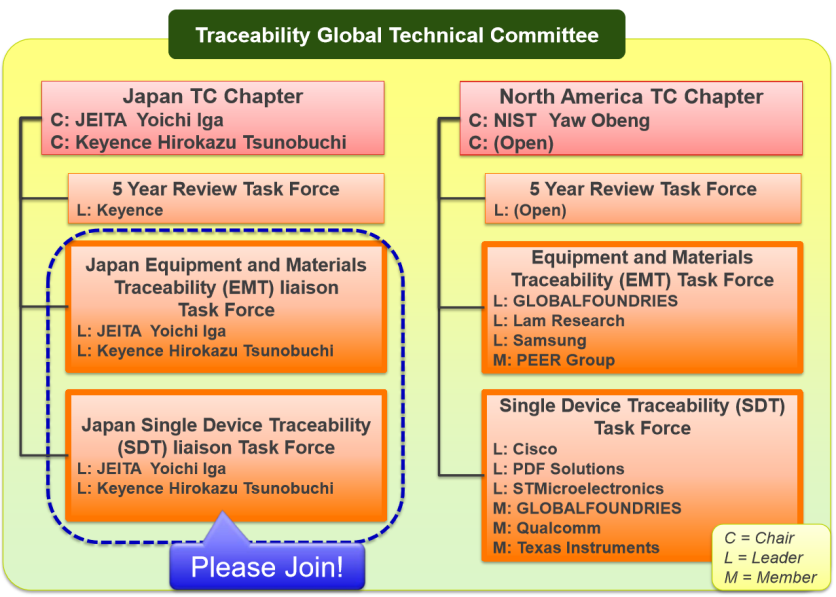

2019年春、トレーサビリティ委員会に設立した2つのタスクフォースの紹介

SEMI スタンダード

トレーサビリティ日本地区技術委員会 共同委員長:角淵弘一(株式会社キーエンス)

2019年6月25日

2018年夏、トレーサビリティ北米地区技術委員会において、2つのタスクフォース(TF)が結成されました。Single Device Traceability(SDT)TFとEquipment and Material Traceability(EMT)TFです。トレーサビリティ日本地区技術委員会では、その2つのTFに対するカウンターパートであるTFの設立を今年4月10日に行いました。それらの活動においてどのようなスタンダードを開発しようとしているのか、それらのスタンダードはどのような背景で必要とされているのかを解説いたします。

半導体デバイスは、航空機・医療機器・通信機器(5Gを含む)・自動車などにおいて幅広く使用されています。それらの用途では、半導体デバイスが社会インフラや人命を背負っているといっても過言ではありません。半導体デバイスに異常が発生すると、社会インフラがダウンしたり、人命にかかわる問題となります。半導体デバイスに対する信頼性がますます高まっています。

しかし、現在多くの偽造半導体デバイスが世界中に流通し、大きな問題を引き起こしています。偽造半導体デバイスの流通金額は年間$7.5bilionドルに達すると報告されています。その影響は、軍需・航空・鉄道・医療の分野に急速に広がっており、危機を拡大させています。

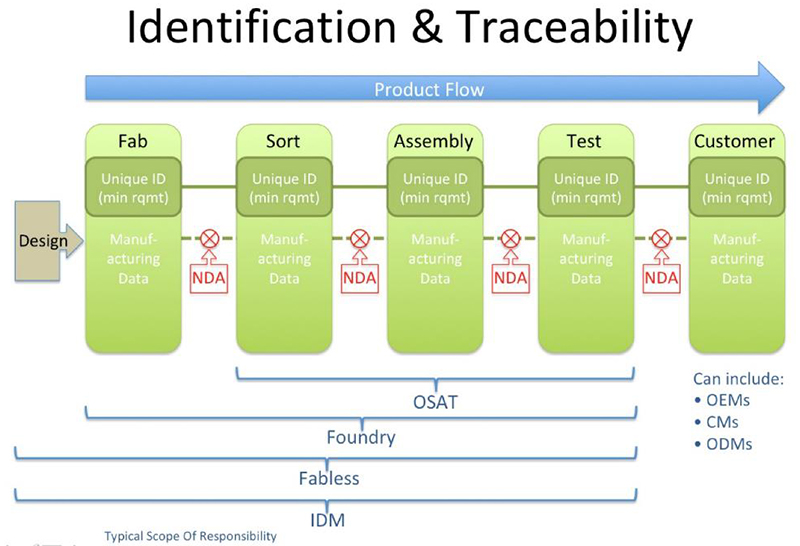

一方で、近年多くの半導体デバイス製造は、以下のように分業化が進みつつあります。

回路デザイン:デバイスメーカ、前工程:ファウンドリー、後工程/テスト工程:OSAT、販売:多数のリセーラー

それらのサプライチェーンは、国を超えて実施されています。偽造半導体デバイスの多くは、これらサプライチェーンのいずれかの段階で巧みに混入されています。

今後、半導体デバイス市場やそれらが使用される全市場が健全に発展するためには、偽造半導体デバイスが製造され市場に流通されない仕組みを作ることは必須であるといえます。1つの企業が行動を起こしても、偽造半導体デバイス問題は決して解決しません。業界が力を合わせて知恵を絞り仕組みを作り規律を守ることが必要です。しかし、現在、偽造半導体デバイスを阻止するためのスタンダードは存在していません。昨年、トレーサビリティ北米地区技術委員会が結成した2つのTFは、まさに、偽造半導体デバイスの流通を大幅に削減し、安全で正しい半導体デバイスを製造し流通する仕組みを実現するスタンダードを作るものです。そしてトレーサビリティ日本地区技術委員会は、同様に、その問題を重大に認識し、北米地区のカウンターパートとして2つのTFを設立しました。

Single Device Traceability(SDT)とは

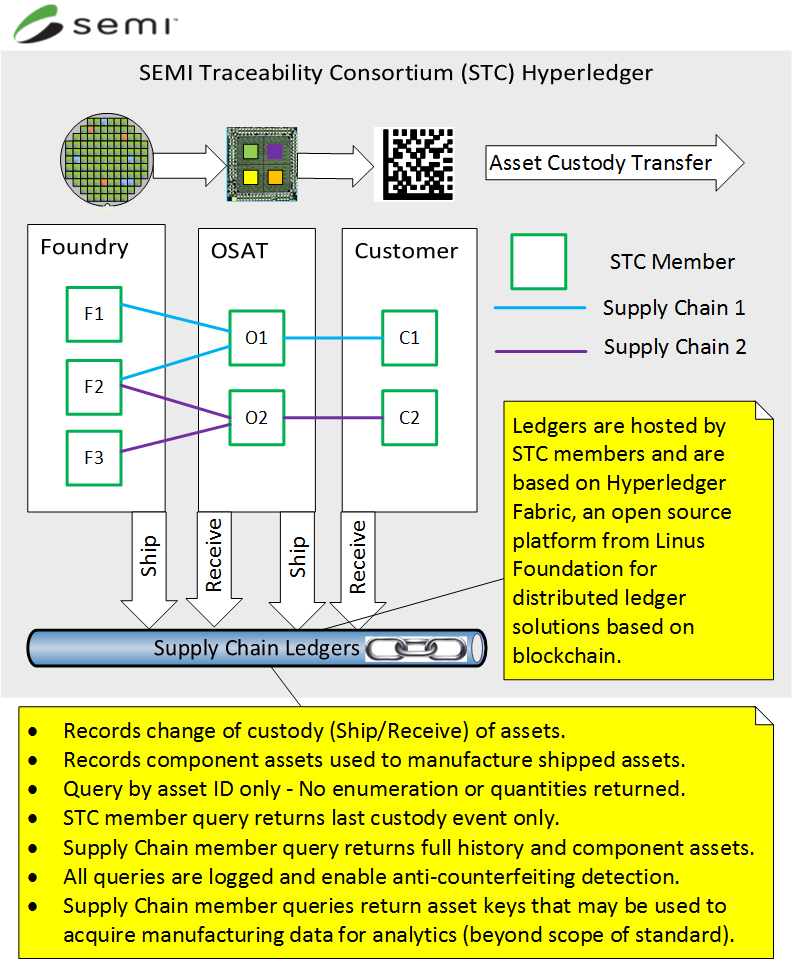

デバイスサプライヤがデザインした半導体デバイスを、ファウンドリー、OSATで正しく製造されていることを確認し、市場で正しく流通されていることをトレースすることを目的とした活動です。トレーサビリティを実現するために、個体識別を行う二次元コードなどの自動認識技術、インターネットを安全に活用する通信技術などにおいて、互換性が高く多くの企業が運用できるスタンダードを作成します。すでにSEMIスタンダードとして出版されている以下の文書を活用し、目的を達成するためにさらに新しいスタンダードを開発することを目指しています。

- SEMI T19: Specification for Device Marking

- SEMI E142:Specification for Substrate Mapping

昨年2018年、このTFが開発を始めた文書Doc. 6450が、今年1月に、SEMI T23: Specification for Single Device Traceability for the Supply Chainとして出版されました。このスタンダードでは、運用するために定義されるべき項目がまだ不足しています。今後、さらに追加されていく予定です。

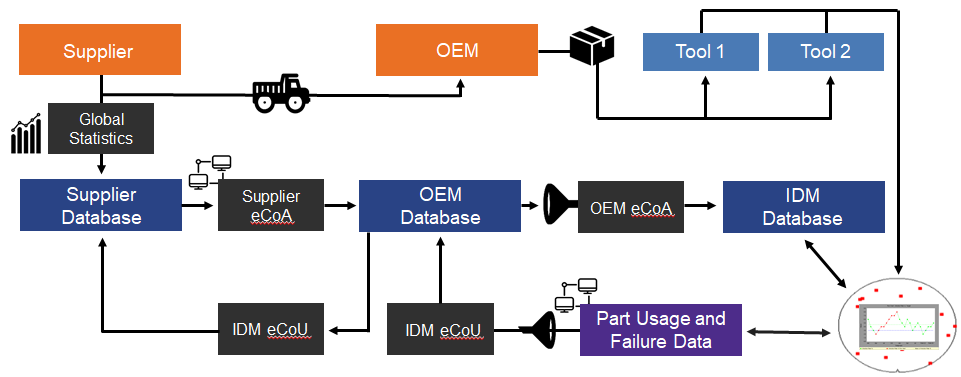

Equipment and Material Traceability(EMT)とは

半導体デバイスメーカがデザインしたデバイスが正しく製造されるためには、以下の条件が整っている必要があります。

正しい設備・サブシステム・消耗部材を使用して製造していること

正しい部材や部品を使用していること

現在、多くの半導体デバイスがファウンドリやOSATで製造されています。それらの製造条件が正しくない場合、製造された半導体デバイスは、性能や寿命などにおいて欠陥を引き起こします。半導体デバイスが正しいかどうか判断されるため、製造・部材情報は工場からデバイスメーカに伝えられ確認されなければなりません。しかし、現在、デバイスメーカがそれらの情報をトレースすることは困難です。

前述のように、偽造半導体デバイスが広まっている中、半導体デバイスの市場やそれらが使用される全市場が健全に発展するために、製造・部材情報をトレースする仕組みの必要性が高まっています。このTFでは、それらのトレーサビリティを実現するためのスタンダードを策定していきます。

このTFが今後新たに開発するスタンダードは、すでに存在している以下のスタンダードを活用します。

- SEMI T7:Specification for Back Surface Marking of Double-Side Polished Wafers with a Two-Dimensional Matrix Code Symbol

- SEMI T9:Specification for Marking of Metal Lead-Frame Strips with a Two-Dimensional Data Matrix Code Symbol

- SEMI T15:Specification for Jig ID: Concept

- SEMI T19:Specification for Device Marking

- SEMI T3:Specification for Wafer Box Labels

- SEMI G83:Specification for Bar Code Marking of Product Packages

Image source: The PEER Group Inc.

これら2つのTFは、半導体デバイス、製造装置、その装置で使用するサブシステムや消耗部材、デバイスを製造するために使用される部材などのトレーサビリティを実現するためのスタンダードを開発します。それらのデバイス・部材・搬送箱・容器などには自動識別するコードを付与します。すでにSEMIスタンダードで使用されているものはそのまま利用し、必要に応じてさらに新たなコードも作成します。そしてそれらの情報はインターネットを経由して、共有されるべき対象者において使用され、トレーサビリティを実現します。そのために必要なデータフォーマットや通信方法についてもスタンダードを開発する予定です。

このような大きな変革をもたらすTFへ皆様の参画をお待ちしております。

本件に関するお問合せ

SEMIジャパン スタンダード&EHS部 柳澤智栄(cyanagisawa@semi.org)