5nmへの道:微細化に付きまとう課題 — 性能対コスト

SEMI デブラ・フォーグラー

半導体業界では、テクノロジーノードの移り変わりに伴う課題や議論に事欠きません。Chipworksのシニアテクノロジーアナリスト、ディック・ジェームズ氏は、「リソグラフィには常に課題が付きまといます」と述べています。7nmに向けてはEUV以外のロードマップもあるかもしれませんが、5nmの登場で何が起きるかは定かではありません。ただし同氏によると、「業界が5nmに到達する頃には、シリコンが限界に達する」ことは明らかです。克服しなければならない今後の課題としてジェームズ氏が挙げているものは、新素材の統合、小型化するコンタクトの接触抵抗、ピッチの4分割、コンタクトのエッチングとセルフアライメントビア、ゲートスタックの縮小、仕事関数材料の変更と多岐にわたります。しかも、これはほんの一部にすぎません。

「目下のところ、FDSOIかFinFETかという点で大きく意見が分かれています。IBMが残ればFDSOIへの道をたどるかもしれませんが、他社はFinFETを選ぶと思われます。ただしこれは、7nmや5nmが実現する頃にはもはや重要な問題ではなく、ナノワイヤなど何か別の手段が必要になるでしょう...最終的には、性能対コストの問題になります」と、ジェームズ氏はSEMIに語りました。

性能と微細化に関しては、FDSOIの権威であり、SOIベース技術の明確な支持者であるSoitecデジタルエレクトロニクス部門SVPのクリストフ・マレビル氏が、極めて低い消費電力を維持しつつ十分な性能の向上を達成することが重要課題であると、SEMIに語っています。SEMICON West 2014で講演者として登壇する同氏は、「PC時代には、性能が最優先でした。消費電力も確かに重要でしたが、高い周波数を得るためにはリーク電流の増加も許されました。ただし、常時オンのモバイルデバイスの時代が到来したことで、優先度が変化しています」と述べました。モバイルアプリケーションが業界をけん引する中、放熱性やバッテリー寿命も性能として考慮に入れる必要があります。「大きな駆動電流を供給することも1つの手段であり、この点ではFinFETが適していると思われますが、アプリケーションにおけるチップの実際の性能に影響を与えるほかのパラメータと照らし合わせて検討しなければなりません」

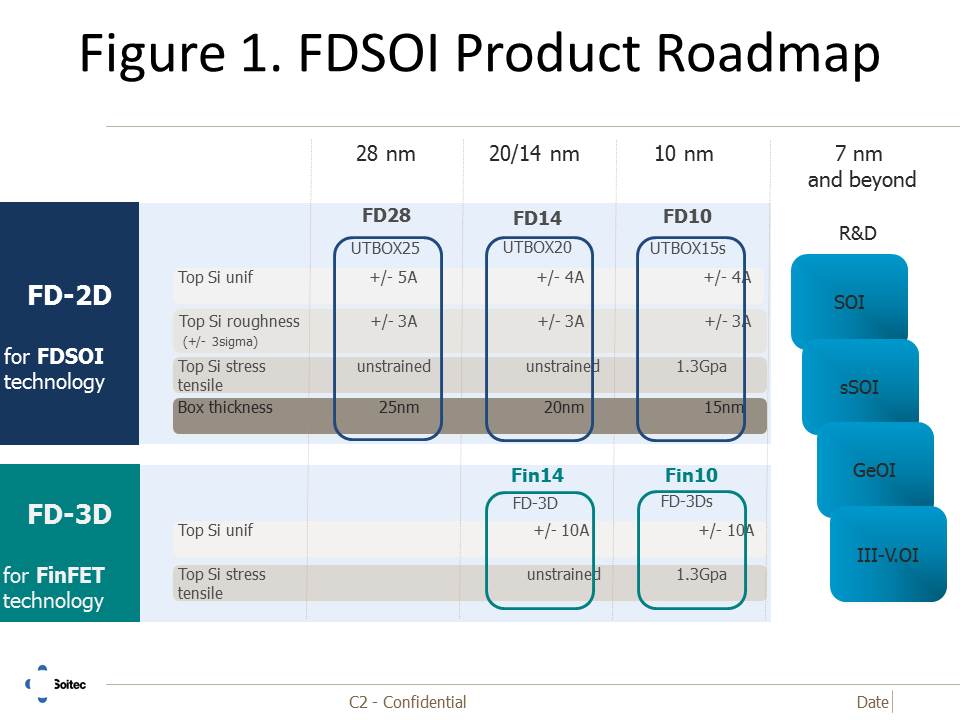

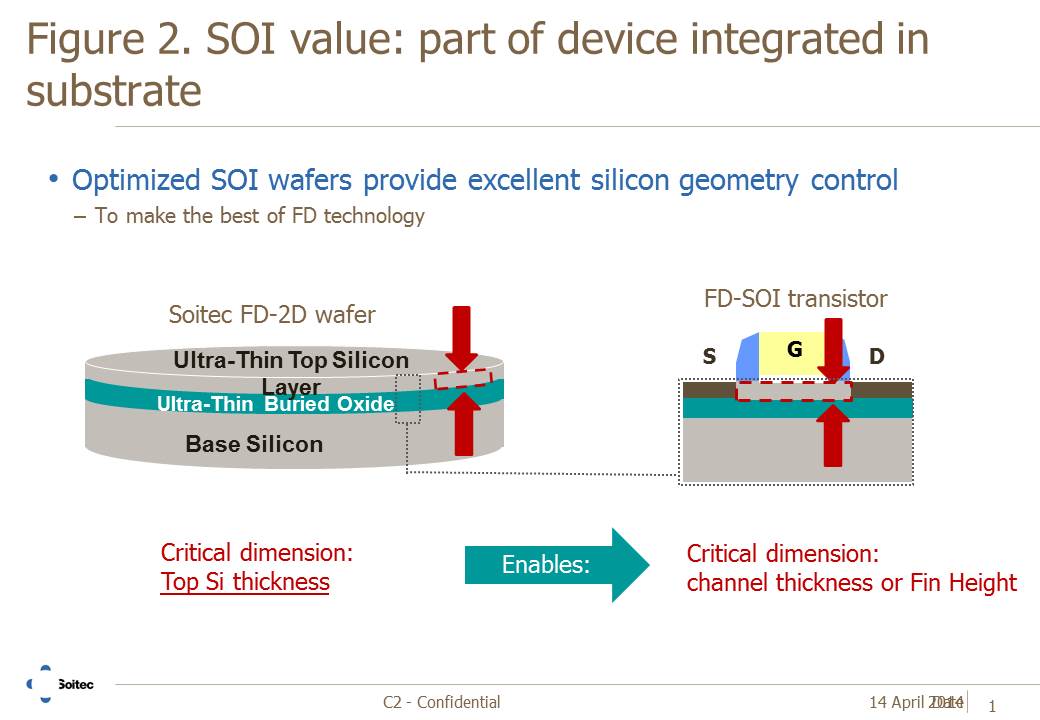

FDSOI技術にも課題がないわけではありません。「FDSOIトランジスタの静電気制御は原則的に、マルチゲートデバイスのものほど優れていません。一方、FinFETでは微細化に伴って寄生容量の削減やばらつき(トランジスタジオメトリのばらつきが原因のものも含む)の抑制などの対策が必要になりますが、FDSOIではそうした対策をとる必要が少なくなります」と、マレビル氏は説明しています。図2に、FD-2D技術においてシリコンのジオメトリ制御や均一性の面でSOIがもたらす価値を示します。

マレビル氏によると、14nmに向けたFDSOI技術による微細化については、IEDM 2013で素晴らしい結果が報告されており、また、LetiとSTMicroelectronicsは、チャネルへのGeの採用、ソース/ドレインのさらなる最適化、オプションでのストレインドSOIの使用を盛り込んだ、10nmに向けたFDSOIのロードマップを発表しています。現在進行中として同氏が挙げたSOIウェーハに関する主な作業分野は、次の通りです。1)薄膜シリコン層における優れた厚さ均一性を確保。これはノードの進化に応じて改善が必要となります。2)旧世代のノードに比べて埋め込み酸化膜の厚さを削減。3)各ノードで求められる最高水準の欠陥制御性を備えた極薄トップシリコン層を引き続き提供。

マレビル氏の説明によると、格子のミスマッチが原因で、シリコン上におけるGeやIII-V族のエピタキシャル成長は実行が難しく、十分な材料品質の確保も困難です。スマートカットベースの層転写による代替手段にも課題(欠陥制御性など)はありますが、「転写層以外では欠陥があるかもしれないドナーから高品質の層をスライスできる利点があり、さらにこのドナーは複数回にわたって再利用が可能です」

CNTの登場

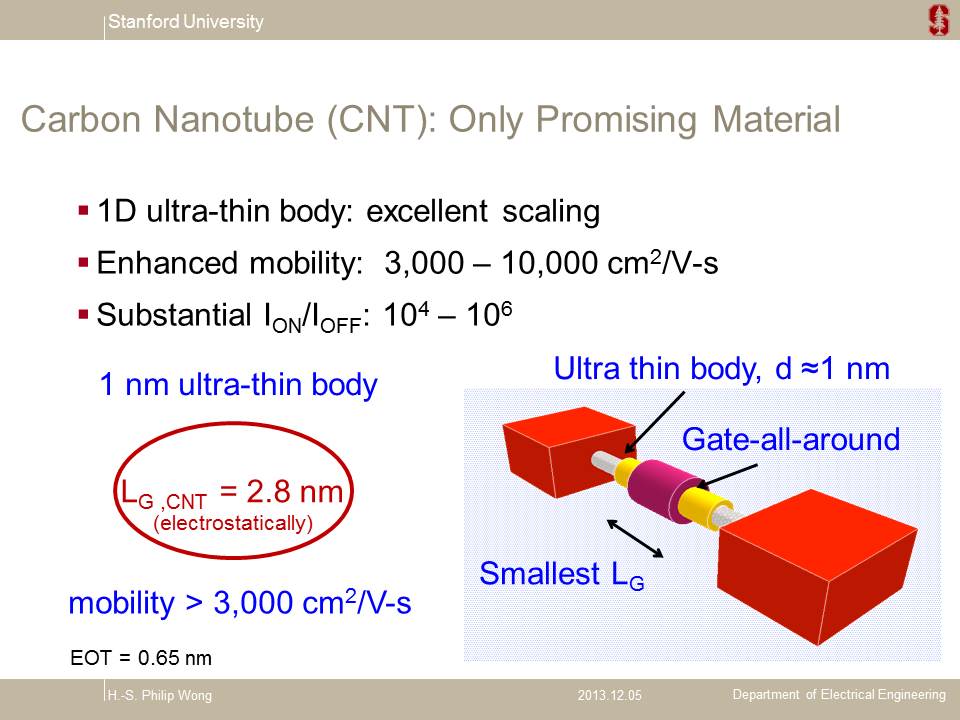

リソグラフィ技術、トランジスタアーキテクチャ、材料の選択肢が無数にあふれる業界において、5 nmに達したときには何か革新的なものが必要になると専門家は述べています。現在注目を浴びつつある技術の1つがカーボンナノチューブ(CNT)ロジックトランジスタです。スタンフォード大学工学部のWillard R. and Inez Kerr Bell Professorであり電気工学教授であるH.S. フィリップ・ウォン氏は、チャネル材料としてCNTを使ったトランジスタが大いに有望であるとSEMIに語りました。CNTの本体はわずか約1ナノメートルと極めて細いにもかかわらず、優れたキャリア輸送特性を備えていることがその理由です。「カーボンナノチューブトランジスタではゲート長を極限まで短くできますが、ほかのバルク半導体にはこうした利点がありません」と、同氏は述べています(図3)。

デジタルロジック向けに最近開発されたCNTトランジスタ技術としては、ウェーハスケール上へのフルアライメントCNTの統合、高性能CNTトランジスタのデバイス製造、3D統合型CNT回路、CNTトランジスタの低電圧(0.2V)動作、コンパクトな回路シミュレーションモデルなどが挙げられます。従来型のCMOSを使用したCNTトランジスタの性能ベンチマークがデバイスレベルとフルチッププロセッサレベルで実施され、回路およびシステム全体の実証も済んでいます。

5 nmノードに向けた業界の動向についてご興味を持たれた方は、SEMICON West 2014のSEMIテクノロジーシンポジウム(STS)セッション「Getting to 5nm Devices: Evolutionary Scaling to Disruptive Scaling and Beyond(5nmデバイスへ:進化的微細化から分裂、そしてその先へ)」でSoitec、imec、Intermolecular、SEMATECH、スタンフォード大学、G450Cの講演をお聞きください。本プログラムの詳細と参加費については、www.semiconwest.org/stsをご覧ください。SEMICON West 2014は、7月8~10日に米国サンフランシスコのモスコーニセンターで開催されます。

その後のSEMICON展示会およびカンファレンスとしては、SEMICON Taiwan(9月3~5日)、SEMICON Europa(10月7~9日)、セミコン・ジャパン(12月3~5日)が予定されています。

(初出 Solid State Technology)