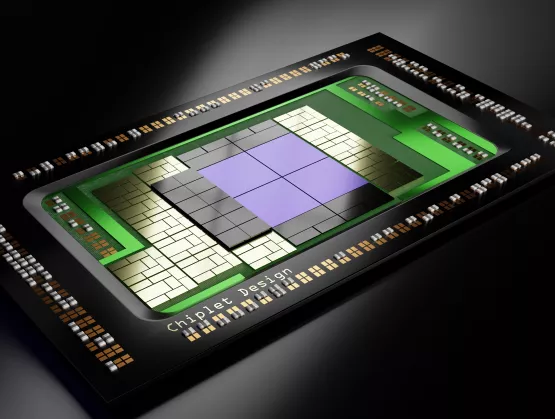

先進封裝技術的進步,讓IC設計者得以將系統單晶片(SoC)裡整合的各種功能分拆成小晶片(Chiplet),再藉由封裝技術將其整合成一顆元件。許多大廠都在近幾年大力擁抱這種晶片設計概念,並在近幾年陸續將其運用在自家產品上,因而讓Chiplet成為半導體業內的熱門關鍵字之一。

但Chiplet的風行,也讓半導體產業必須有所調整,以建構出對應的完善生態系統。日月光集團研發中心副總暨SEMI封裝測試委員會主席洪志斌就指出,如果從更宏觀的角度來看,半導體產業發展的方向,其實是追求更高效的系統整合。系統整合又可分成兩種HI,一種是同質整合(Homogenious Integration),另一個則是異質整合(Hetrogenious Integration)。我們在發展對應的實作技術之際,另一方面也要持續強化、深化產業鏈成員的合作,才能克服這條路上遇到的種種挑戰。

Chiplet已成大勢所趨

研究機構TechSearch總裁Jan Vardaman指出,Chiplet不僅讓IC設計者可以更靈活地實現自己想要設計的晶片,同時也讓晶片製造的成本變得更便宜。因為不同功能電路可選用最具性價比的製程技術來生產,不必全部採用最先進製程。

由於Chiplet可以帶來更高的靈活性與更好的成本結構,近幾年市場上出現許多採用Chiplet架構的元件。但目前市場上的Chiplet產品,是各家大廠自行發展出來的成果,故目前半導體業內存在多種不相通的Chiplet互連技術,導致Chiplet生態系呈現碎片化的局面。以打破藩籬為訴求的UCIe標準,是Chiplet生態系一個重要的發展里程碑,但不會是所有問題的解答。

超微(AMD)先進封裝部門企業副總裁Raja Swaminathan則認為,市場需求是推動半導體產業轉向異質整合的關鍵因素之一。高效能運算市場對處理器效能的需求,已無法光靠製程微縮來滿足。做為處理器供應者,AMD必須找出新的方法來滿足客戶。Chiplet是這個問題的有效解法。藉由Chiplet,晶片成本跟元件尺寸微縮的問題有了解決的方法,讓該公司能夠推出符合市場需求的產品。

日月光院士既資深技術顧問William Chen(Bill)則認為,要進一步推動Chiplet生態系發展的關鍵,在於如何將產業的研究成果轉移到教育體系。目前與Chiplet有關的設計方法、技術,都掌握在業界手中,學生在教育體系裡面沒有機會接觸,導致熟悉Chiplet設計的人才養成相當困難。而人才對於半導體產業的發展極為關鍵,因此我們必須設法讓更多學子在學校裡面就開始接觸Chiplet,才有助於Chiplet的進一步普及。

益華電腦(Cadence)研發副總裁Don Chan則表示,Chiplet是IC設計領域的重要典範轉移。藉由將SoC解構成Chiplet,再透過先進封裝技術將其整合成一顆元件,IC設計者一直在追求的效能、功耗與面積(PPA)三大設計目標,有了新的實現路徑。但這個趨勢也為IC設計者帶來新的挑戰,例如原本整合在SoC裡的功能應該如何拆分、如何設計多顆Chiplet間的互連架構、以及晶片堆疊後最棘手的散熱問題等。這些新挑戰都需要對應的設計流程、方法論與工具來支援。

針對當前業界最熱門的Chiplet概念,聯發科製造營運副總經理高學武分享了該公司的產品開發經驗談。高學武指出,對IC設計者而言,Chiplet最有趣,也最有價值的地方在於,這個概念讓IC設計變得像在調雞尾酒,只要調和不同的素材,就能實現出獨特的產品。另一方面,市場對下一代產品的要求越來越高,只靠一顆晶片上的電晶體預算,已經無法滿足客戶對功能跟性能的要求。因此,藉由晶片切割(Die Partitioning),把客戶期望的功能分成多顆晶片來實現,是唯一的解法。

而在這個設計實踐的過程中,聯發科也發現,Die Partitioning確實可以帶來節省成本的效果。因為有部分功能可以用較成熟、性價比更高的製程來實作,而且個別晶片的面積也變小了,讓聯發科得到更漂亮的良率數字。

晶片散熱亦為主要挑戰 浸泡式冷卻充滿潛力

雖然以先進封裝來整合Chiplet,已成為半導體技術重要的發展趨勢,但困擾半導體業多年的散熱問題依然存在,而且在先進封裝時代只會變得更加複雜,同樣需要創新的解決方案。

緯穎科技總經理張順來就表示,緯穎做為一家伺服器製造商,會出現在半導體業者雲集的異質整合國際高峰論壇,就是因為散熱的問題需要產業鏈上下游通力合作,才能更有效地解決。緯穎近年來一直大力發展浸泡式冷卻方案,就是因為晶片產生的熱量已無法只靠風扇移除,同時也直逼液冷技術的極限。把整張主機板連同上面的電子元件全部浸泡在冷卻液裡,是未來必然要走的路。

但目前半導體元件所使用的封裝技術,並未針對浸泡式冷卻做出最佳化設計,因此,張順來希望能與封裝產業的夥伴進行深度合作,例如在封裝上預留讓冷卻液可以通過的孔道,來增加浸泡式冷卻技術的散熱效率。

解決傳輸功耗問題 CPO技術不可或缺

值得注意的是,在晶片元件裡,除了運算、儲存單元會產生熱,負責傳輸資料的I/O單元,也是不容小覷的熱源之一。且隨著運算效能不斷提升,帶動I/O頻寬增加,I/O的功耗問題也變得越來越具挑戰性。

思科(Cisco)副總裁Jie Xue就指出,由於網路資料量無止境的成長,網通晶片的I/O頻寬要求也越來越高。但傳統的傳輸介質已無法在可接受的功耗水準下,承載這麼大量的資料,因此網通ASIC採用矽光子(Silicon Photonics)這類Co-package Optics(CPO)技術來實現,已經是大勢所趨。

CPO是一種典型的異質整合,藉由先進封裝技術將使用CMOS製程的邏輯單元跟採用特殊製程的光電、光學元件整合在一起,晶片開發者不僅可以獲得更多通訊頻寬,而且傳輸資料時所消耗的電力也大幅減少。正因為擁有這些優勢,CPO已成為網通相關晶片未來的發展方向。

台積電分享CoWoS技術家族最新進展

除了國際大廠的分享外,台灣晶圓代工龍頭台積電亦現身說法。分享其CoWoS技術家族的最新進展。

台積電APTS/NTM處長鄭心圃指出,為滿足高效能運算領域的客戶需求,台積電多年前就發展出CoWoS先進封裝技術。歷經多年發展後,如今CoWoS技術已經擴張成一個技術家族,有許多不同的衍生版本。會發展出不同的技術,是因為不同的客戶有不同的偏好,有些客戶特別看重效能,有些則希望高密度導線,有些希望有成本效益。

例如,原本使用矽中介層的CoWoS,後來衍生出以有機中介層取代矽中介層的CoWoS-R。因為低阻抗的導線CoWoS-R在反應速度和耗能上均更佳, 亦可進㇐步整合去耦電容被動元件,讓晶片的整合度更上㇐層樓,適合大功率的系統整合。

設備/材料廠聚焦混合接合 各家競推解決方案

作為封裝產業最重要的年度論壇,除了前面提到業者外,矽品、應材(Applied Materials)、科林研發(Lam Research)、EVG、Brewer Science等重要產業鏈成員,也都在今年的論壇上,分別從Chiplet整合所使用的先進封裝技術選擇,以及相關設備、材料等環節切入,介紹其所提出的解決方案。

在今年的論壇上,混合接合(Hybrid Bonding)無疑是最重要,也最被反覆提及的議題。為了將互連線路跟接點的尺寸作得更細小,滿足先進封裝對互連密度的極致要求,每家投入先進封裝技術的業者,都選擇了混合接合這條技術道路。但混合接合本身對製程條件的要求,例如接合面的潔淨度、材料的物理特性等,都有十分嚴格的要求。因此,要將混合接合運用在量產上,雖已不成問題,但還是有許多充滿挑戰性的技術議題存在。

挑戰之所在,也就是商機之所在。誰能為混合接合所遇到的技術挑戰提出解決方案,就能抓住龐大的市場商機。這或許也正是混合接合相關議題,之所以在今年的異質整合國際高峰論壇上一再出現的原因。從設備、材料到檢測/計量,為不同製程環節提供方案的業者,都提出針對混合接合製程開發的新解決方案。