SEMI met with Gerald Beyer, program manager at imec, to discuss the co-existence of various 3D interconnect technologies and their need for new materials and integration solutions. The two talked in the runup to his presentation at the Advanced Packaging Conference at SEMICON Europa 2018, 13-16, November 2018, in Munich, Germany. To register for the event, click here.

SEMI: Can you confirm this trend towards heterogeneous integration and do you think it will be a long-term development trend?

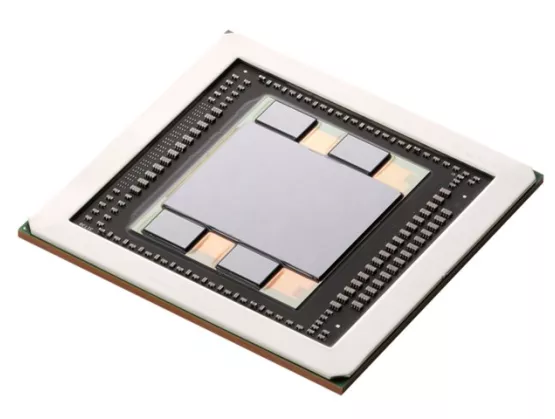

Beyer: We consider heterogeneous integration as a scaling booster for functional partitioning and as a fashion method to create systems, which would not be possible or economical on such as a single chip. As you can apply it to numerous systems, we expect it to stay for the long term.

SEMI: What are the new critical challenges for the combination of different technologies into one package?

Beyer: When you create a complex system, there is usually more than just one challenge. On one side, you need to be able to design such a system. If you disintegrate a large chip, you need to decide how to reconstruct it, i.e. which function goes into which strata. You would like to do that not manually but with a set of tools supporting the designer. Only recently EDA (Electronic Design Automation) and design houses have started to support this idea.

On the technology side, interconnections between some strata of such a reconstructed chip will require small pitch interconnects of the order of 1µm pitch and less. Today, wafer-to-wafer bonding technologies have sufficient overlay margins for 1µm pitch. Wafer-to-wafer bonding technologies, however, have a number of constraints such as equal die size and the necessity to realize chip stacking rather in a fab environment than in a traditional packaging house. Die-to-wafer assembly technologies still need to bridge the gap to deep sub 10µm pitch in terms of alignment and cleanliness.

![]()

SEMI: What kind of new materials or integration solutions do you expect to be developed? Are you working on it already?

Beyer: As explained above, die partitioning requires sub 1µm pitch interconnects. We are investigating fine pitch wafer-to-wafer and die-to-wafer (direct) bonding. For the latter, not only new alignment capabilities but also die cleaning and thin die handling technologies need to be developed. To build a complete system with data processing, memories etc., novel integration schemes such as Flip Chip – Fan Out Wafer Level Packaging with high density 2D and 3D interconnect capabilities are being investigated.

These new systems differentiate from current ones by high density Through Package Vias (TPV), Si bridges and sub 2µm line/spacing RDL. The new integration approaches push the materials such Temporary Bond Materials (TBM), Wafer Level UnderFill’s (WLUF), photo patternable polymers for fine Line/Spacings to name a few, to the limits. Hence, development of new materials is a key aspect.

SEMI: What trends and developments do you expect in the near future and why would you recommend attending the Advanced Packaging Conference?

Beyer: The development and commercialization of products using heterogeneous integration is a big effort drawing on resources from EDA vendors, materials and packaging tool suppliers, OSATs, foundries, memory suppliers and IEDMs and academia alike. The agenda of the Advanced Packaging Conference at SEMICON Europa reflects this diversity and I am looking forward to interesting discussions with all participants.

Gerald Beyer has been working in the field of 3D Technologies since 2012 as the technology program manager of the 3D System Integration Program of imec. Prior to this role, he was the interconnect program manager and group leader of BEOL integration. He received a PhD in materials science from Imperial College, London and a MSc from Thames Polytechnic, London.

Serena Brischetto is a marketing and communications manager at SEMI Europe.