leti Ceatech

# Frugal Artificial Intelligence

78.1413

### **Thomas Signamarcheix**

Vice President Strategic Development, CEA-Leti

and preserve the planet

Mobile data + 20316%

Internet traffic +1170%

Electricity + 22%

Internet users +125%

World population +10%

Sources: Worldometers 2021, enerdata 2021, ourworldindata.org Internet 2021, Cisco Visual Networking Index 2011 & 2020, Ericsson Mobility report 2021

## DIGITALIZATION

> Providing great new services

Smart home

Smart cities

Agriculture

Health

Factories

Energy networks

**60B**

~

connected objects by 2030 using embedded computing

CHALLENGE INNOVATION WILL BE KEY FOR ENVIRONMENTAL SUSTAINABILITY

Committed to innovation, CEA-Leti's dedicated teams pioneer micro-nanotechnologies enabling smart, energy-efficient and secure solutions for industry

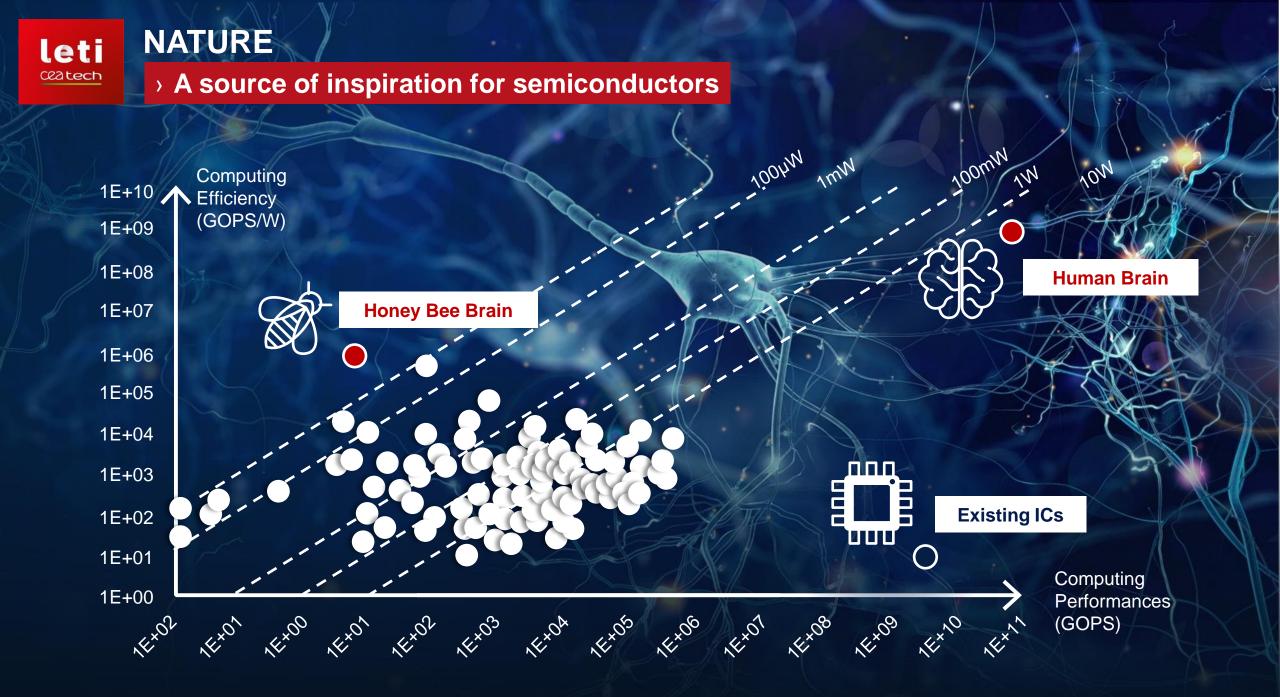

### Al is a promising field but a lot of research is still needed:

- Local training > Local inference

- Incremental learning > PetaOPS/W

- > Multi-sensor platform

- Frugal computing

## Image: Sector Sector

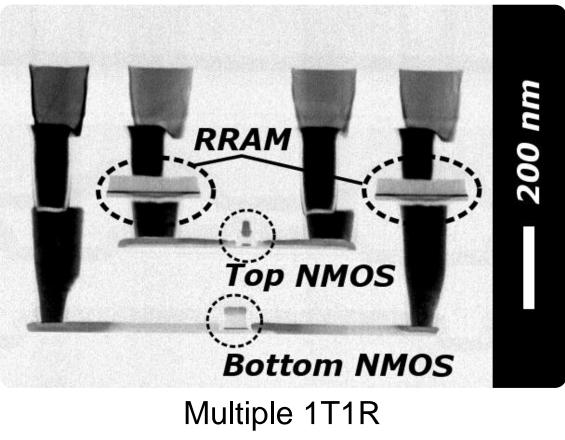

#### **RESISTIVE MEMORIES**

> Efficient back-end of line implementation

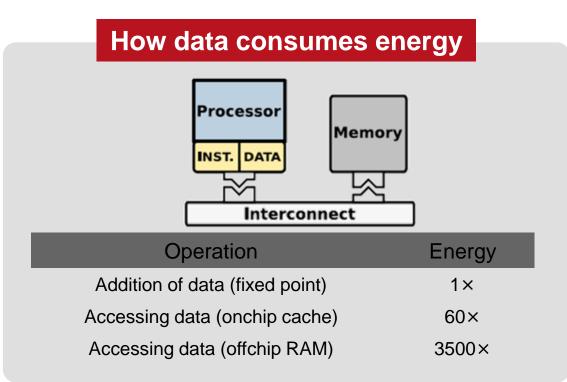

Data movement between storage and processing units can reach 90% of the overall energy consumption Image: descent and descent and

**Non-volatile memories**

Need for high density on-chip resistive memories

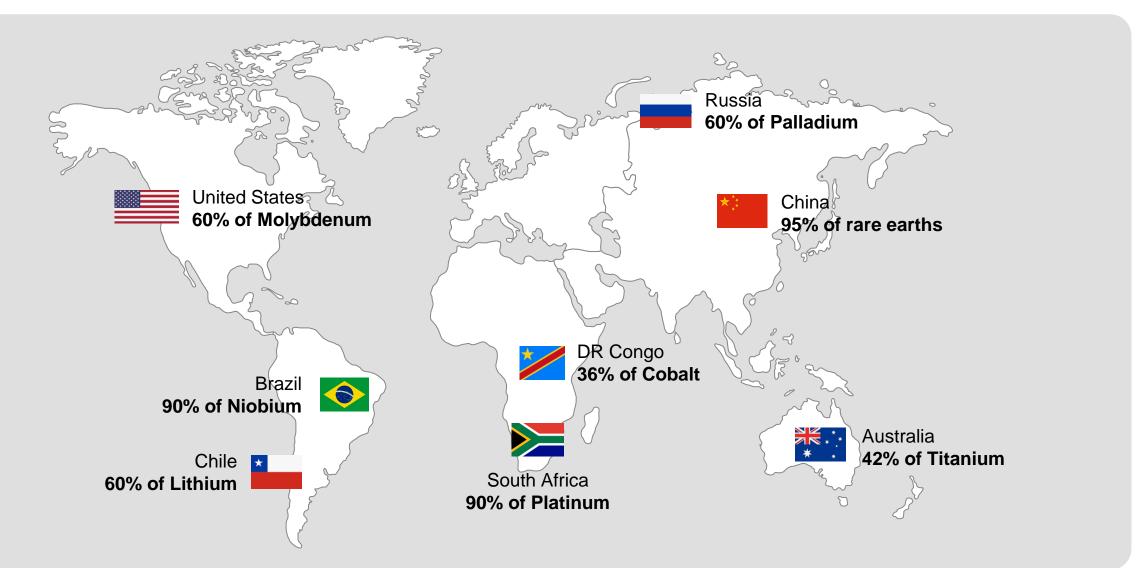

#### **RARE EARTHS AND MINERALS**

> A small number of countries control the production

## GREENER SEMICONDUCTOR TECHNOLOGIES

**Hf** Hafnium

### DIFFERENT TYPES OF MEMORIES

| the second        | reduction × 20,000                |                                   |                           |

|-------------------|-----------------------------------|-----------------------------------|---------------------------|

|                   | FLASH                             | ReRAM (HfO <sub>2</sub> )         | FeRAM (HfO <sub>2</sub> ) |

| Programming power | ~200pJ/bit                        | ~100pJ/bit                        | ~10fJ/bit                 |

| Write speed       | 20 µs                             | 10-100 ns                         | 14ns @ 2.5V               |

| Endurance         | 10 <sup>5</sup> - 10 <sup>6</sup> | 10 <sup>5</sup> - 10 <sup>6</sup> | > <b>10</b> <sup>11</sup> |

| Retention         | > 125°C                           | > 125°C                           | 85°C                      |

| Extra masks       | Very high (>10)                   | Low (2)                           | Low (2)                   |

Programming power

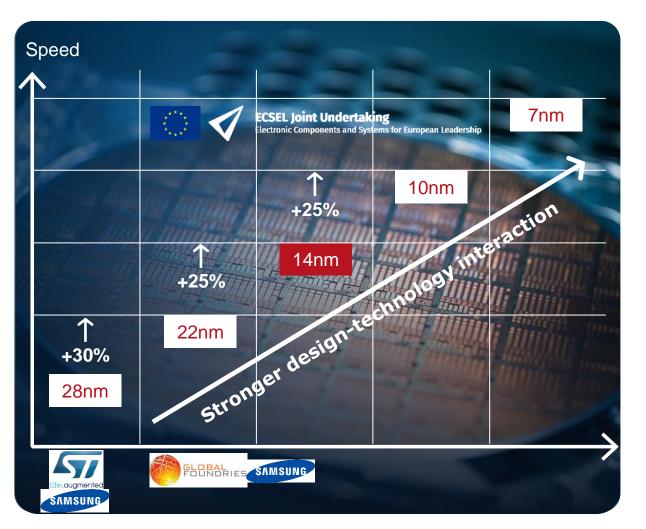

## Scaling the FD-SOI technology is becoming indispensable

- > ultra-low power IoT devices,

- > automotive,

- > RF,

- > Edge AI,

- > 5G-6G

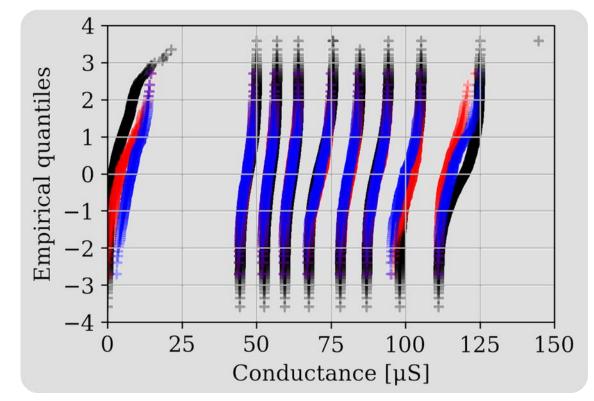

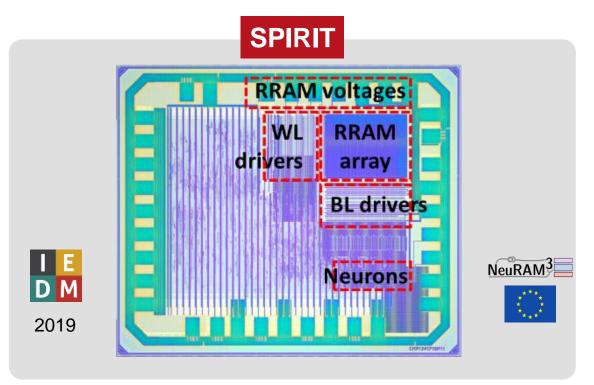

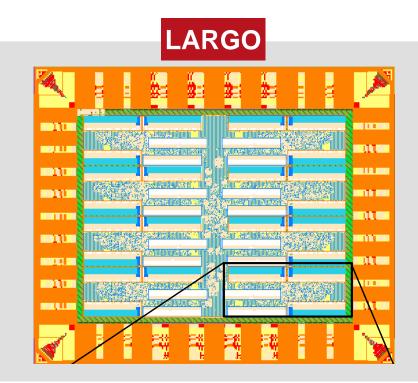

#### **RESISTIVE MEMORIES**

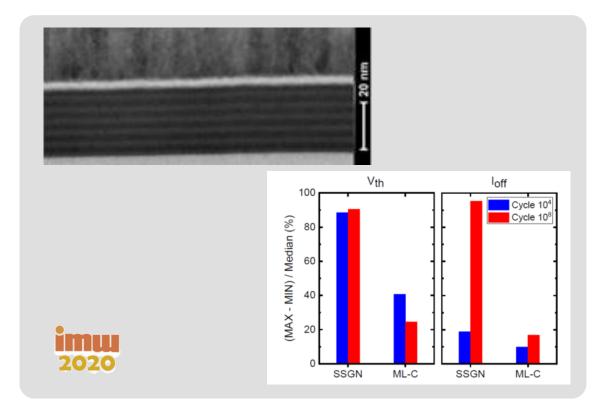

> Analog behavior of resistive RAM

1.5 × area gain

Multi-Level-Cell

3.17 bit per RRAM

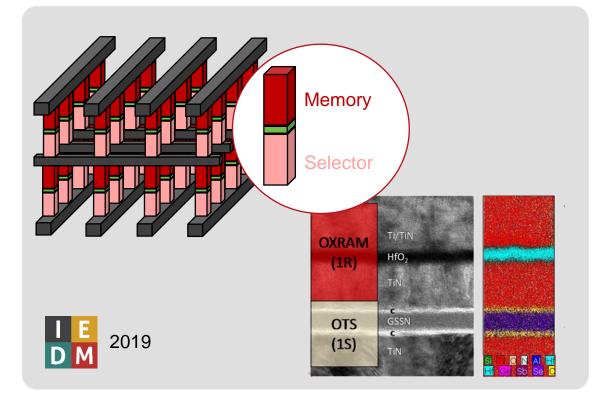

#### **Ovonic Threshold Switch**

Ovonic Threshold Switch Multilayer Architecture

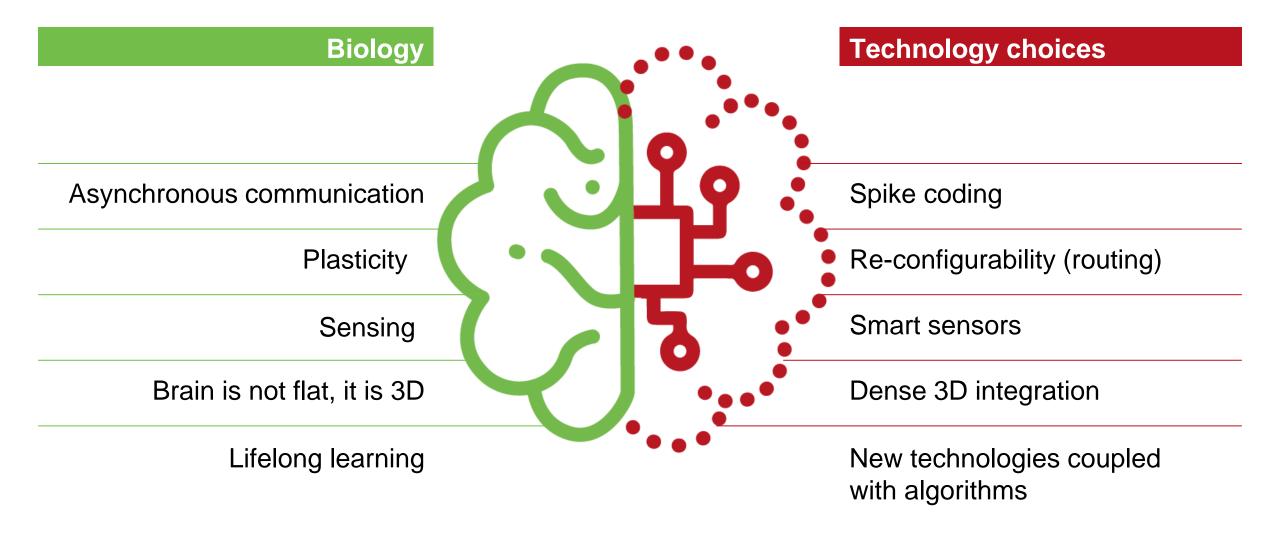

#### **SPIKE CODING**

> Toward sub pJ / event efficiency

CMOS node: 130nm 10 neurons & 144 synapses 3.6 pJ /spike

CMOS node: 28nm (FD-SOI) 131k neurons & 75M synapses 0.5pJ / spike

## 1010100010111017401040100061

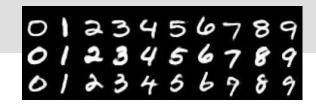

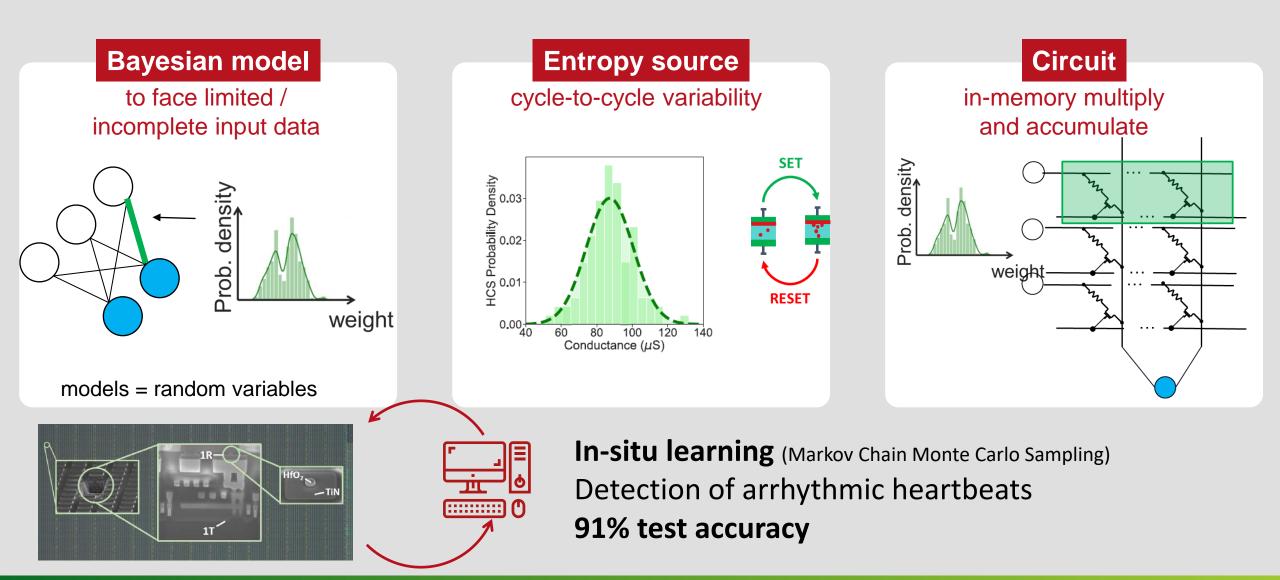

## The brain deal with noisy devices

without any error-code correction...

> Embracing the statistical nature

of emerging memories

#### **Deterministic model**

'You have input a 3'

## The "small-data" world has a lot of uncertainty

'The input looks most like a 3... but I am very uncertain about that'

### nature electronics

2021

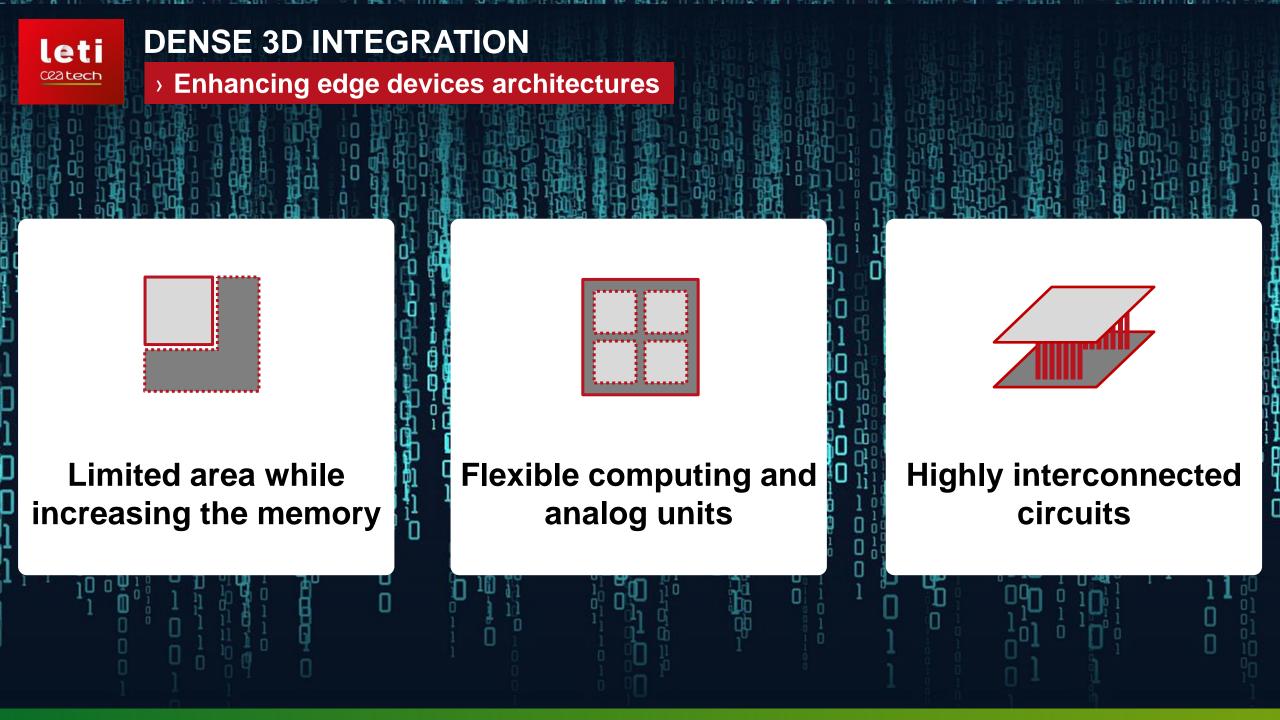

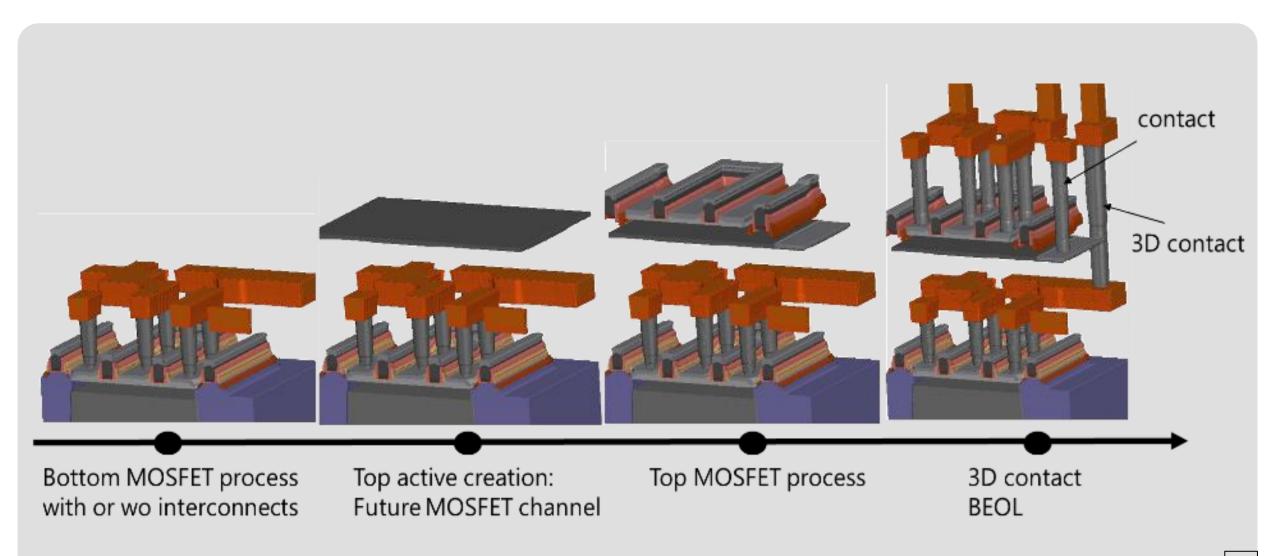

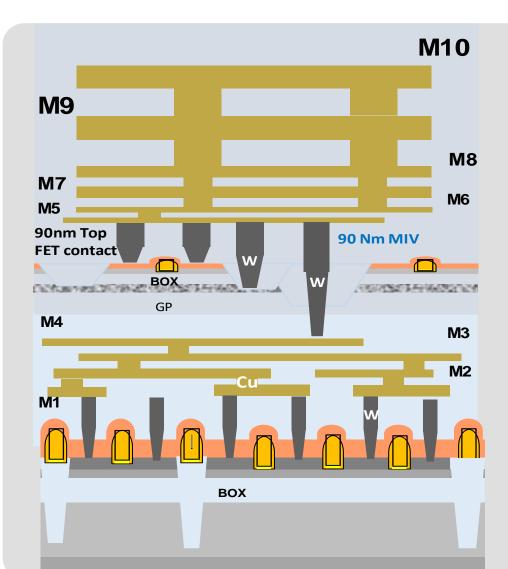

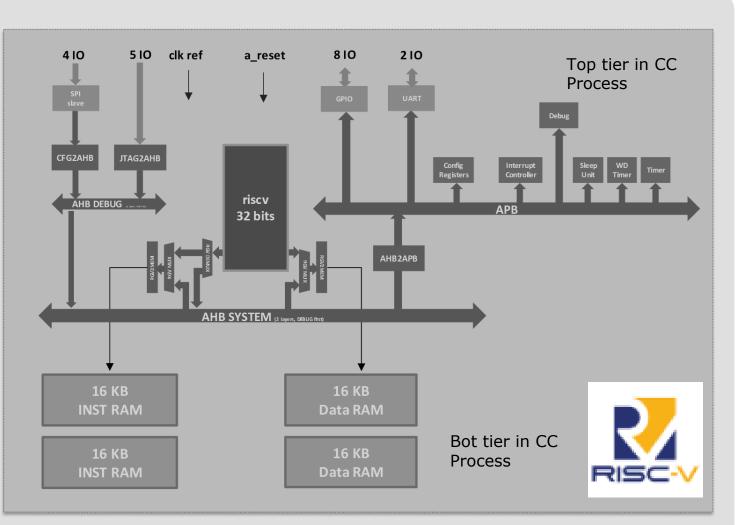

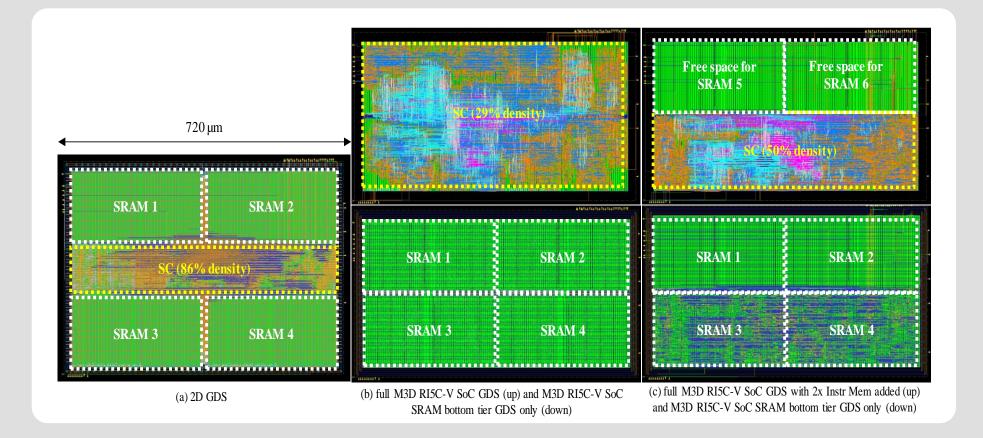

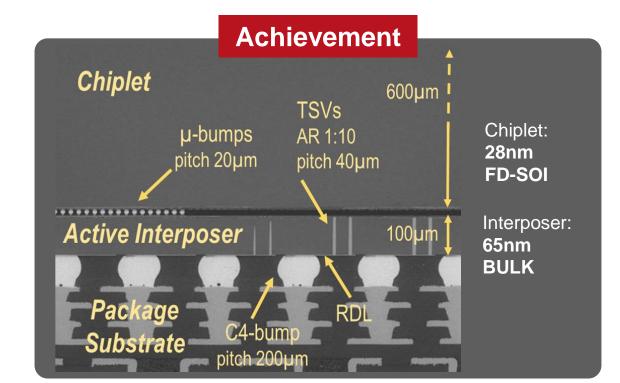

#### **DENSE 3D INTEGRATION**

#### > Enhancing / Optimizing circuits footprint

leti

#### **DENSE 3D INTEGRATION**

#### > Enhancing / Optimizing circuits footprint

> 23% area reduction

> 7% performances improvement

> 8k-415k Intermediate Vias

> 2x local inst. memory Increase

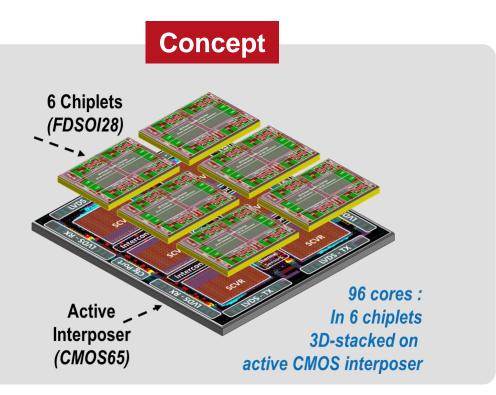

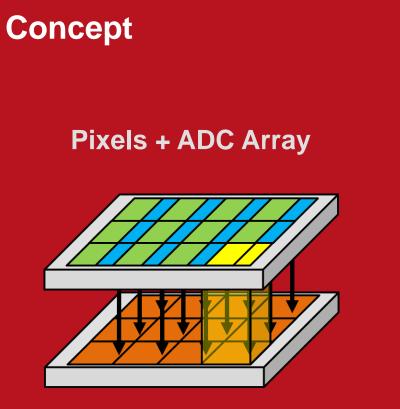

#### **DENSE 3D INTEGRATION**

> Flexible computing and analog units

Improve parallelism, power performance, versatility and cost with a modular architecture based on smaller chips

The power of 10 laptops with a surface of only 200mm<sup>2</sup> 100GOPS, 10GOPS/Watt

Memory + processing

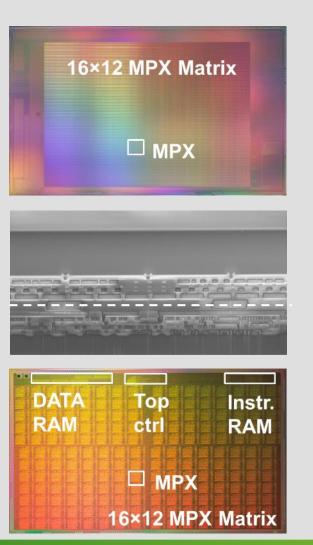

#### **Achievements**

| Node<br>Integration<br>Power cons   | Node          | 130nm                      |  |

|-------------------------------------|---------------|----------------------------|--|

|                                     | Integration   | Stacked BSI*               |  |

|                                     | Power cons.   | 720mW @9b 5500fps          |  |

|                                     |               | 230mW @8b 340fps           |  |

| e<br>L                              | Pixel size    | 12umx12um (subpixel)       |  |

| Resolution<br>Sensitivity           |               | 1024x768                   |  |

| l ů                                 | Sensitivity   | 15V/lx.s                   |  |

|                                     | Dynamic range | 54dB                       |  |

|                                     | ADC resol.    | 10b                        |  |

|                                     |               | 340fps @0.78Mpixels 10bits |  |

| Frame rate                          |               | 1500fps @0.05Mpixel 10bits |  |

|                                     |               | 5500fps @0.05Mpix 9bits    |  |

| Parallelisi<br>PE array<br>Data men | Parallelism   | matrix                     |  |

|                                     | PE array      | 3072                       |  |

| of 1                                | Data memory   | 73kB+98kB                  |  |

| du                                  | Instr. Memory | 65kB                       |  |

| Clock freq                          |               | 80MHz                      |  |

| 0                                   | Performance   | 61Gops @8b img             |  |

#### NEW PARADIGM IS NEEDED TO FAVOR SOBRIETY/FRUGALITY VS. DECLINISM

### We need to drastically reduce the energy

## and environmental footprint of electronic devices

TRENDS

#### Sobriety athlete's approach

Maximize performance for a given resource

## If you share the same vision, Join us!

thomas.signamarcheix@cea.fr

EAC300bi\*rd