# Challenges and Opportunities in Semiconductor Packaging

Oreste Donzella

Executive Vice President, EPC Group

KLA Corporation

November 2021

# Semiconductor Industry

"It's Never Been a Better Time"

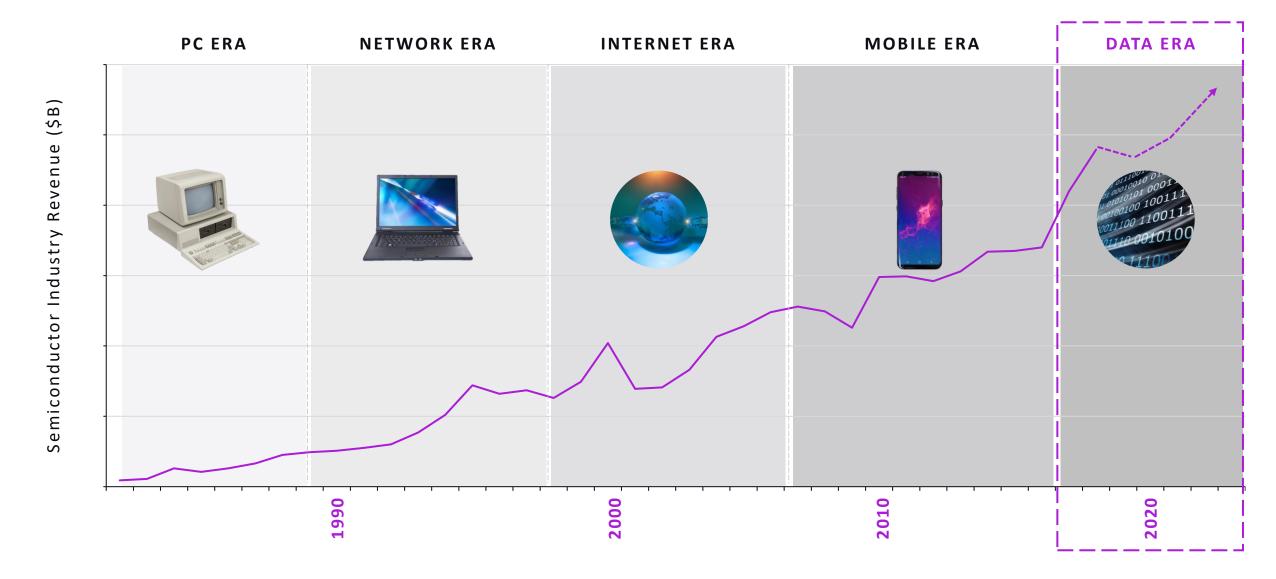

## Semiconductors: Key Enablers of the "Data" Era

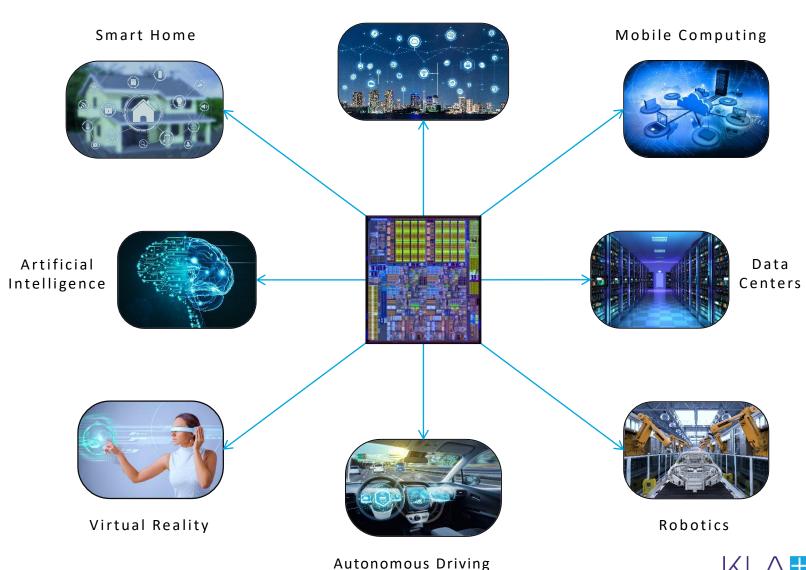

## The Data Era: Unprecedented Number of Market Drivers

#### The Data Era

everything becomes smart producing, storing, analyzing and transmitting an enormous amount of data

Smart Infrastructure

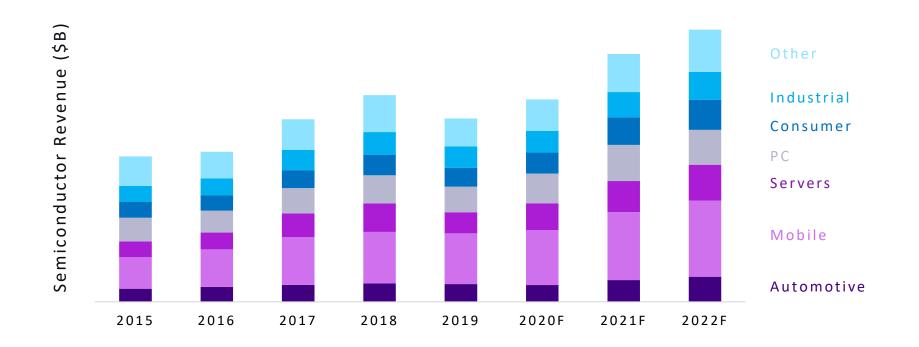

## Semiconductor Drivers: The Secular Story Continues

| Artificial<br>Intelligence | 5G Connectivity | Virtual<br>Interaction | Mobile | Data Center | Automotive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Healthcare |

|----------------------------|-----------------|------------------------|--------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|                            | (((-1))         |                        |        |             | To the second se |            |

Sources: Gartner

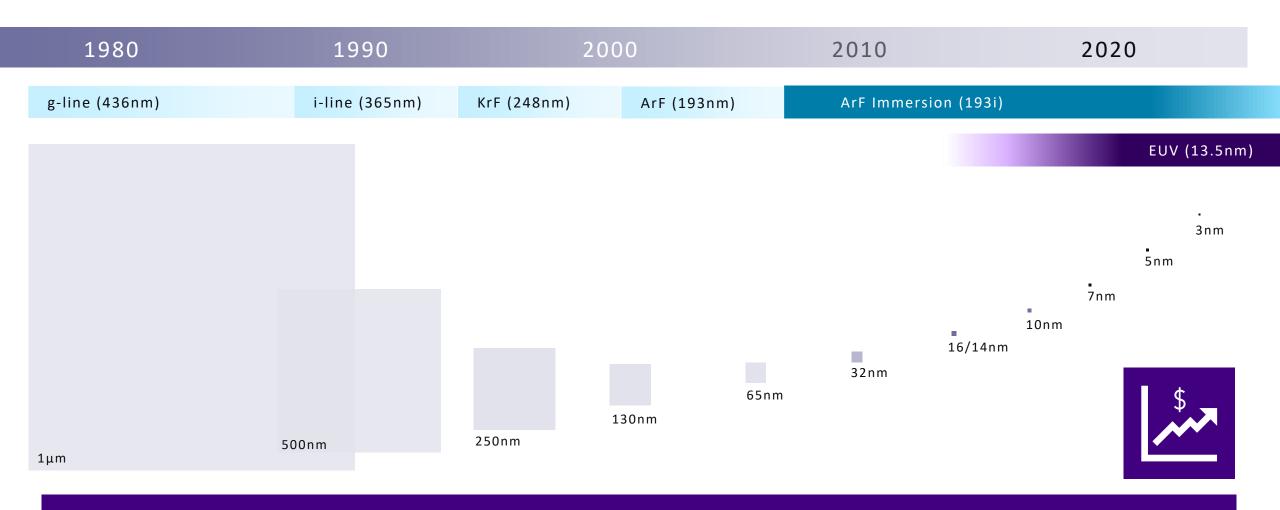

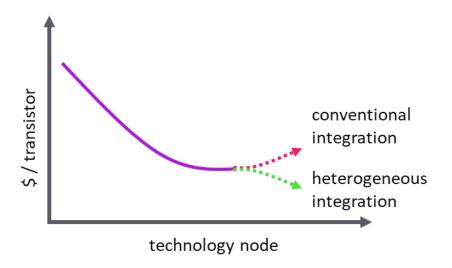

## Semiconductor Technology Scaling for 50+ Years

Conventional Scaling is Still Happening, But it Has Become Too Complex and Expensive

## Advanced Packaging

"Everything is Changing"

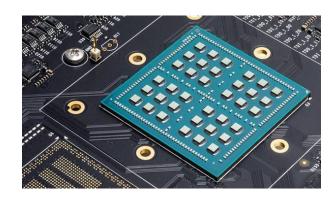

## Advanced Packaging: Crucial to Semiconductor Technology Roadmap

Improved Bandwidth

Boost in Power

Performance

New High-End Applications

Custom Form Factors

Increased Overall Si Area

From Device Protection to Performance Differentiation

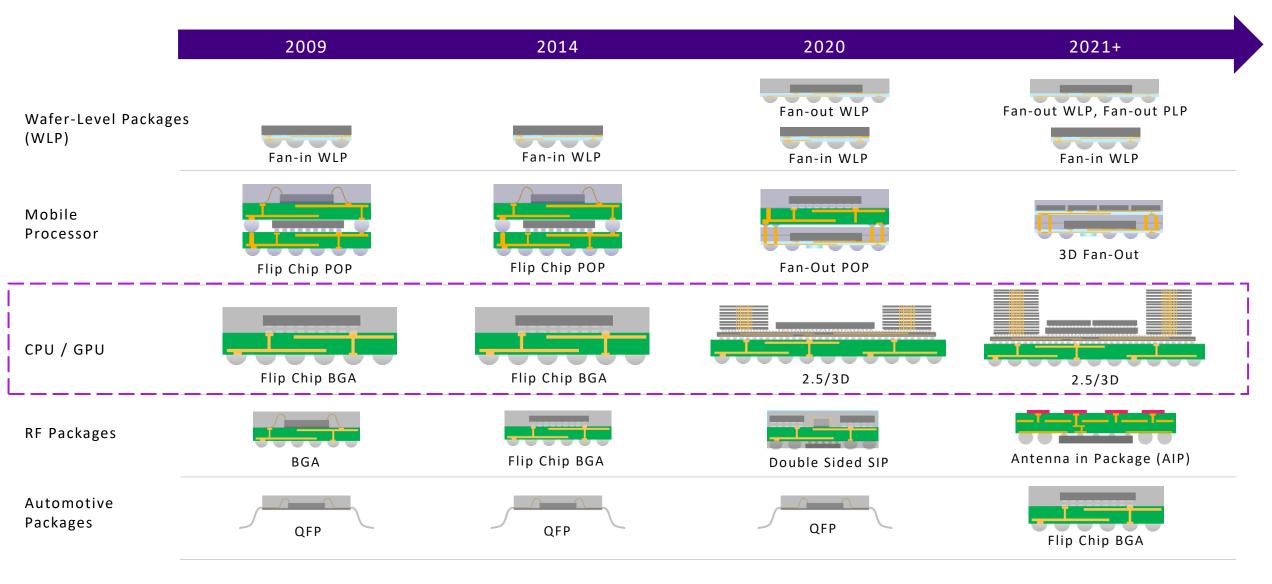

## Advanced Packaging: More Types | Higher Complexity

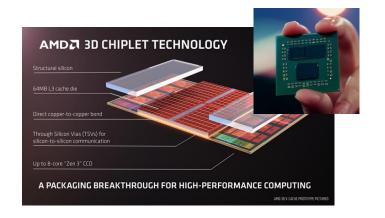

## **Chiplet Architectures**

## Heterogeneous Integration

"The Whole is Greater than then Sum of Parts"

## Heterogeneous Integration: Scaling While Keeping Costs Down

- From system on chip (SOC) to chiplets

- High cost only for core functionalities

- Disaggregation of the non-core functionalities

- Heterogeneous integration via packaging

## The Known-Good Die (KGD) Problem With Chiplets

#### How are defective chiplets escaping?

Function of fab yield and test coverage

Bare die test limitations

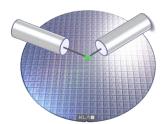

## Chiplet test escapes from wafer sort at 98% test coverage for various escape models

Number of Escapes Depends on Test Coverage and Yield

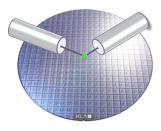

## The Known-Good Die (KGD) Problem With Chiplets

### Expensive challenge with increased die count

#### How are defective chiplets escaping?

Function of fab yield and test coverage

Bare die test limitations

#### Package yield @ 2000 DPPM average chiplet escape rate

Package Yield Lower With Increased Number of Chiplets

## Chiplet Escape Reduction Requires a New Approach

More sophisticated

electrical test binning

#### Chiplet Escape Reduction 100% of lots, 100% of Inline optical inspection die on critical layers Inline defect screening methods already reducing screening for early escapes for automotive chips identification of at-risk devices I-PAT® (Inline Defect Parts Average Testing) Improved wafer sort (including µbump probing) Inline wafer I-PAT analysis of Statistical outlier High risk die identified inspection inspection attributes analysis and screened

Methods to Improve Quality and Reliability for Auto Chips

Can Also Improve Chiplet Package Yield

wafer probe

# **Hybrid Bonding**

Innovative Technology for Heterogeneous Integration

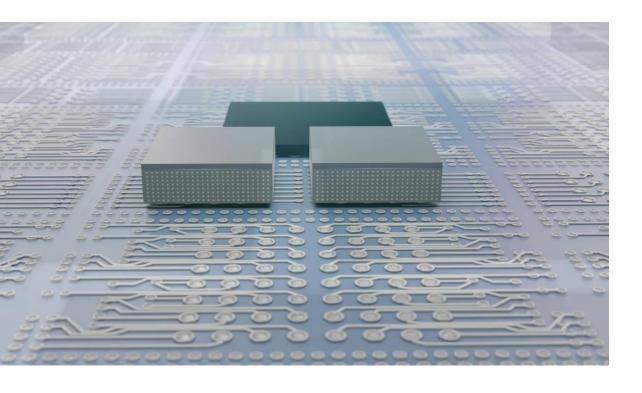

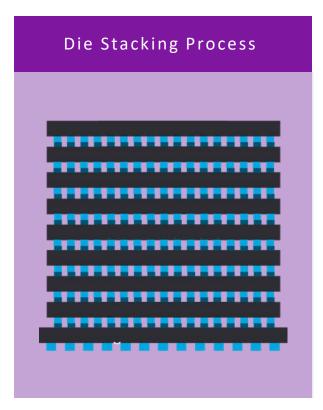

## Hybrid Bonding: The Next Inflection in Heterogeneous Integration

- Key Benefits: Speed, Bandwidth and Power Efficiency through increased interconnect density

- Hybrid Bonding in Packaging with D2W integration key for AI Logic Chips and High Bandwidth Memory

Several Inspection, Metrology and Integration Challenges

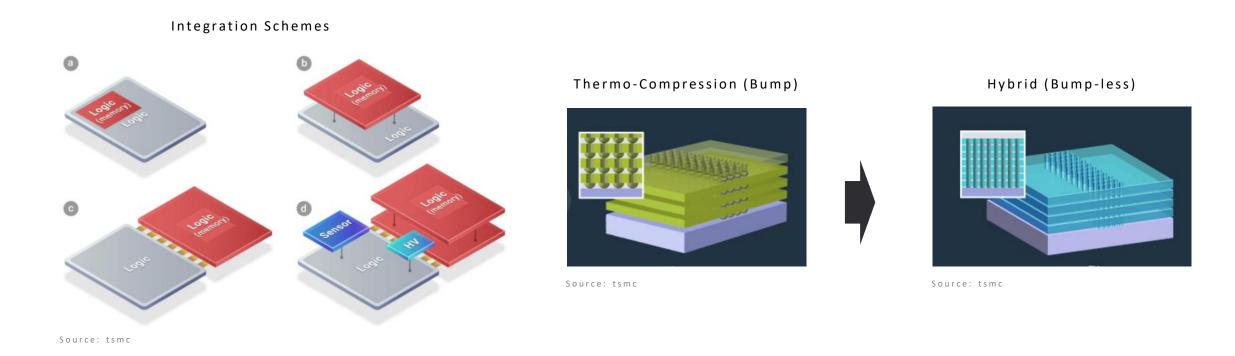

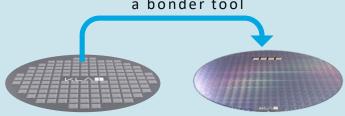

## Die to Wafer Hybrid Bonding Integration Schemes

#### Collective Hybrid Bonding

Die to be bonded are prepared, diced, then placed on carrier wafer

Activation, cleaning and then bonding

Remove carrier wafer, leaving bonded die on target wafer

- Die transfer all at once

- Narrow die thickness range

- Proven die activation and cleaning methods

- Possible rework

- Challenges include thin die, cleanliness, alignment, carrier removal

#### Sequential Hybrid Bonding

Singulated die are transferred to carrier for activation and cleaning

Direct placement of die using a bonder tool

- Die transfer one by one provides flexibility

- No die thickness limitations

- Challenges include handling of multi-die stacks, die activation and cleaning, alignment, cleanliness

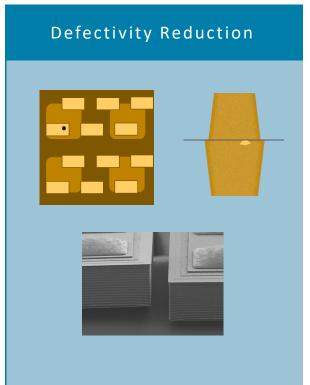

## **Hybrid Bonding Challenges**

#### Surface Cleanliness Before Bonding

- Significantly cleaner surface required compared to thermal compression bonding (TCB)

- Particles/residues cause voiding

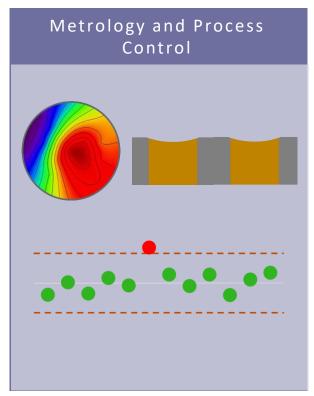

#### Surface Topography Before Bonding

- Cu/dielectric profile critical

- CMP process control

- Current AFM not capable in high volume manufacturing

#### Die Singulation Cleanliness and Final Profile

- Conventional die singulation (laser/saw) very dirty

- Bonding and stacking very sensitive to die profile

#### Low Temperature Processing

- Etch/deposition processes on the presence of soft adhesives

- High-quality but low temp (<125°C) processing capabilities needed

## Collaborations: Key to Tackle the Challenges and Provide Solutions

Several Active Projects with Top Semiconductor iDMs, Foundries and OSATs

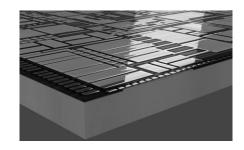

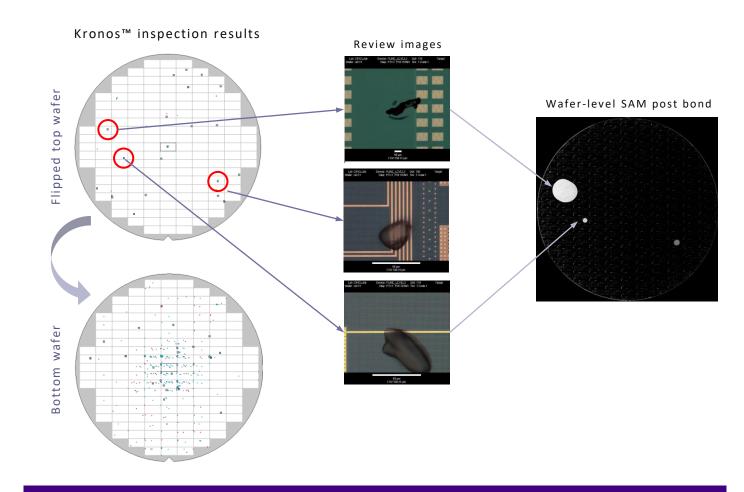

## Surface Cleanliness Before Bonding

# Wafer Inspection Requirements High sensitivity for 3DIC and FO Detect and resolve excursions Bonded, thinned, warped and diced wafers

Post-Bond Void Correlation to Defects

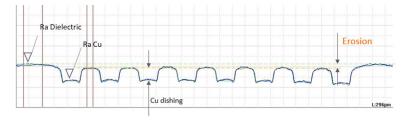

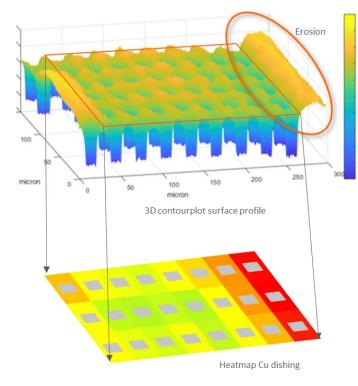

## Surface Topography Before Bonding

#### Metrology Requirements

- Surface profile for hybrid bonding

- Si thickness for TSV process control

- Final revealed TSV height

#### Erosion and Cu dishing in Zeta cross section

Quantify Erosion, Cu Dishing and Roughness

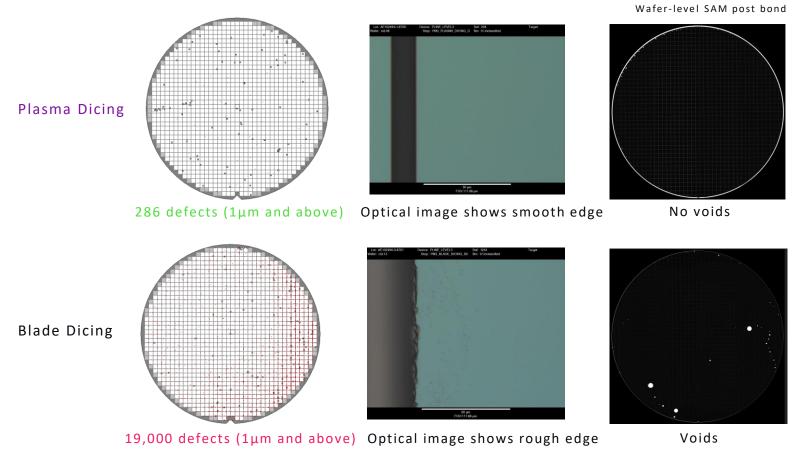

## Die Singulation Cleanliness and Final Profile

# Dicing Requirements Increased die strength Defect free dicing Reduced dicing kerf width

Plasma Dicing Results in Smooth Profile and Low Defectivity

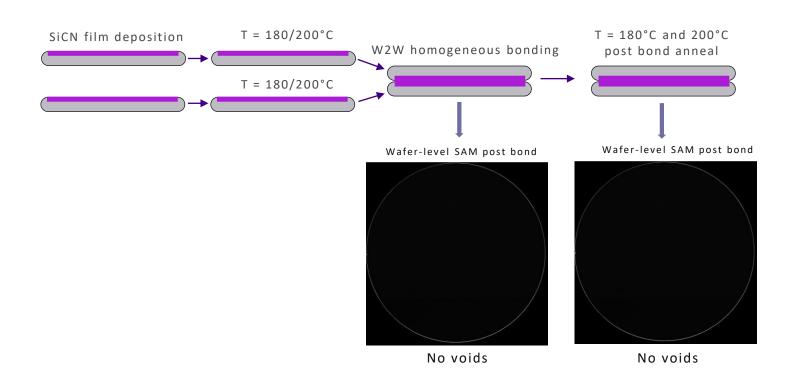

## Low Temperature Processing

#### Low Temp PECVD Requirements

- SiCN films at 175°C and 350°C

- Tunable carbon and stress

- Good thermal stability

- Void free

Low Temp SiCN Films are Void Free After Bond and Anneal

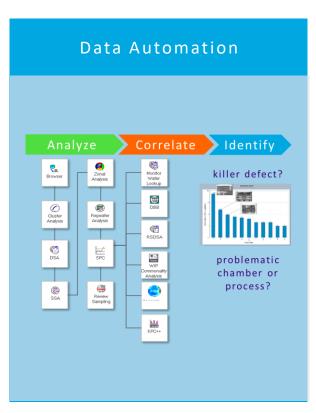

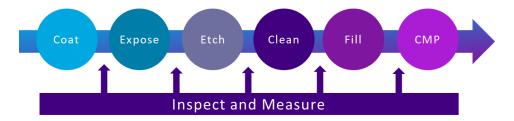

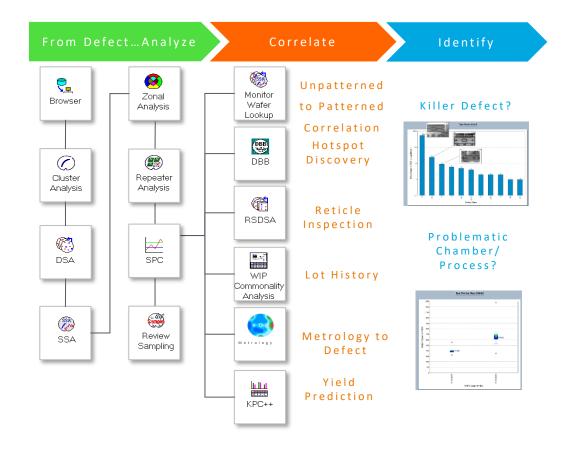

### **Data Automation Solutions**

#### **Process Control**

Introduced in frontend in mid 90's

#### Klarity® Data Analysis System

## Summary

An Exciting Time for Advanced Packaging

## An Exciting Time for Advanced Packaging

- Packaging is driving performance differentiation

- Heterogeneous integration enables scaling

- Chiplets require Known Good Die; established methods from auto fabs can help

- Hybrid bonding technology is driving innovation for both process and process control

## Thank You

Oreste Donzella

Executive Vice President, EPC Group

KLA Corporation

November 2021